Breaking Boolean Shackles with Static Sign-Off

DAC Forum presentation by Prakash Narain, CEO, Real Intent

Overview

Real Intent CEO Prakash Narain presented at DAC on how static sign-off’s “minimally Boolean” approach helps design teams efficiently start verification earlier in the design process.

Below are lightly edited highlights of Dr. Narain’s presentation.

Simulation & formal verification — Limited by Boolean methods

Shift left can be understood as the earliest verification of a design step; the value of shift left is to reduce the cost of each iteration. The driving force behind this shift left is avoiding costly RTL & netlist ECOs and iterations.

Because simulation and formal verification methodologies rely heavily on Boolean analysis, they have a significant limitation for shifting left.

Formal is slow with significant capacity limits for exhaustive analysis, while simulation requires large resource investments.

Static sign-off: Minimally Boolean

For shift left, we need approaches that will produce results faster and early — for that static signoff is the is the best approach.

Static sign-off is only minimally dependent on Boolean methods, so it is not limited by those Boolean shackles.

Static sign-off abstract checking methods

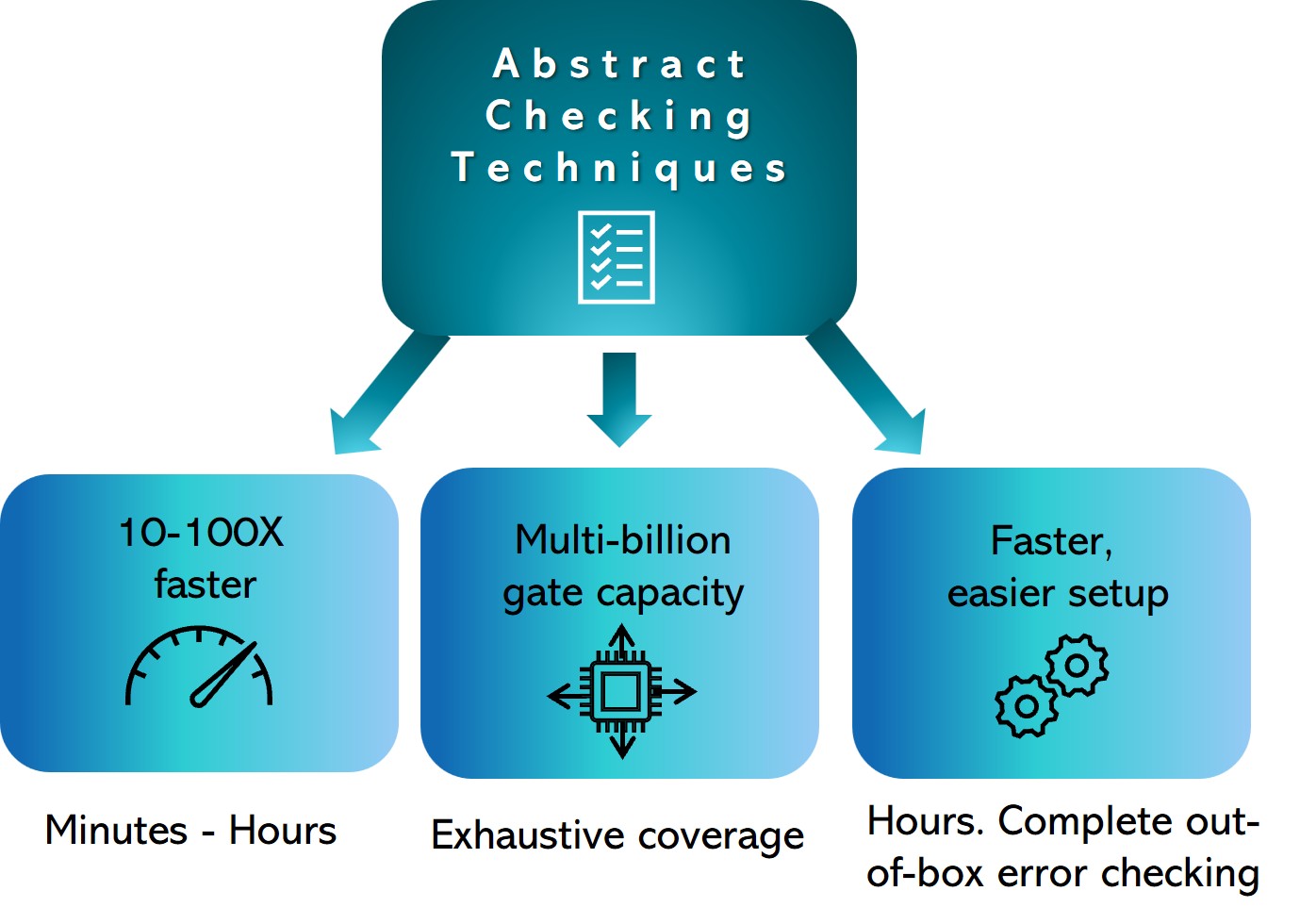

Static signoff builds custom solutions for specific problems, primarily using abstract checking methods. This targeted rule checking is what gives it minimal dependence on Boolean values.

Let’s look at why this is so important.

- First, static sign-off’s analysis time is 10X to 100X faster than formal – it can run a million gates in a few minutes.

- Second, it has the capacity to achieve exhaustive coverage of billions of gates in hours without black-boxing.

- And third, its setup typically only takes a few hours, because it has complete out-of-the box error checking, without the need to write testbenches or assertions.

Further, user-defined rules enable comprehensive analysis across newer applications with evolving design requirements.

Expanding static sign-off applications

This combination of quick set up, blazing fast runtime, and high capacity is why static sign-off has gained traction over the past two decades.

It makes it practical for designers to start functional verification during early RTL design — well before even simulation.

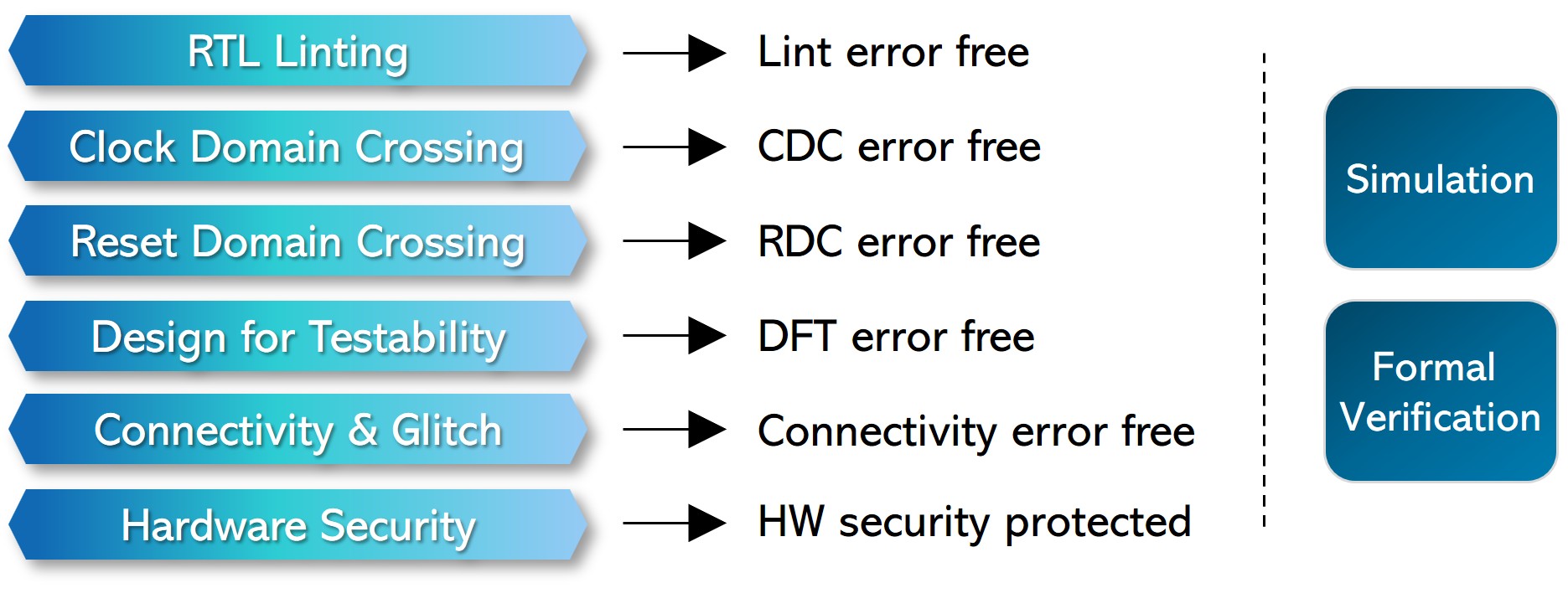

Static sign-off applications have been expanding. They now include RTL linting, clock domain crossing, reset domain crossing, design for testability, connectivity & glitch, and hardware security static sign-off.

Advanced static sign-off methodologies

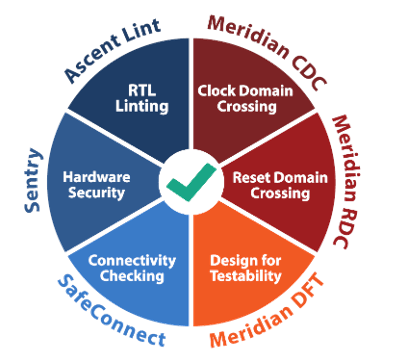

Real Intent currently has offerings across all six areas, with more underway.

With this context, below, multiple Real Intent team members share highlights of advanced, minimally boolean, static sign-off methodologies that we’ve seen our customers leverage across these six static sign-off domains.

RTL Linting

Clock domain crossing

Reset domain crossing

DFT

Connectivity & Glitch

Hardware security