Early RTL Code Linting & Sign-Off

Ascent Lint uses static analysis to enforce coding guidelines, enabling you to catch functional issues early — prior to simulation — and ensure high-quality RTL. It has unmatched performance, targeted debug, and multi-policy runs.

Ascent Lint provides high-impact rules for syntax, semantic, and style checks. The RTL linting rules are designed for low noise and ease of debug. Our intuitive GUI makes rule selection and configuration fast and easy.

Additionally, our integrated debugger provides targeted debugging to facilitate resolving lint issues efficiently.

Built-in, High Impact Rules

Our built-in rules ensure that your designs meet relevant coding guidelines for RTL/Netlist sign-off.

Real Intent derives its RTL linting rules from industry standards, including Reuse Methodology Manual and STARC, and well-researched papers, and provides a built-in policy to enable all of the lowRISC Verilog Coding Style rules.

Real Intent uses its deep expertise to filter out only the relevant rules from these sources. Additionally, the industry expertise we’ve gained based on input from and collaboration with our customers, enables us to ensure our continuously rules keep up with increasing complexity.

Rule Selection & Configuration

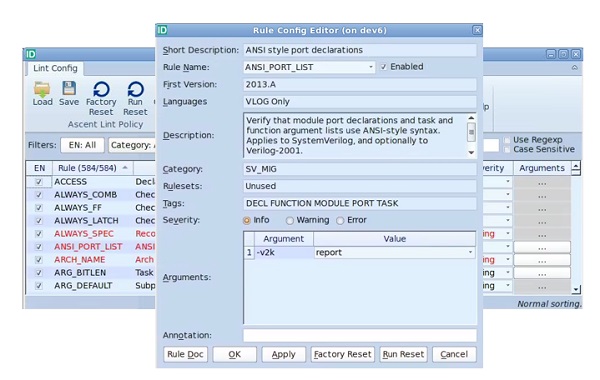

Ascent Lint has a rule configuration editor that makes rule selection and configuration fast and easy.

Rules can be configured to enable variations in behavior based on user preferences. For example, all rules have a “severity” configuration. Severity can be configured based on the severity of the RTL Coding guideline.

All rules also have an “annotation” option that enables adding some text that is printed with the rule description. This can be used, for example, to associate the Ascent Lint rule with the name of the Coding guideline.

The rules are categorized, with filters and searches to make it simple to find the relevant rule.

Ascent Lint Resources

RTL Coding & Safety Standards

Ascent Lint supports all industry HDL standards: the synthesizable subset of Verilog, SystemVerilog, and VHDL. It can also read IP that is encrypted per IEEE 1735. Ascent Lint is ISO-26262 certified by TÜV SÜD, an internationally accredited independent testing and conformity assessment company, enabling immediate integration into ISO 26262 flows.

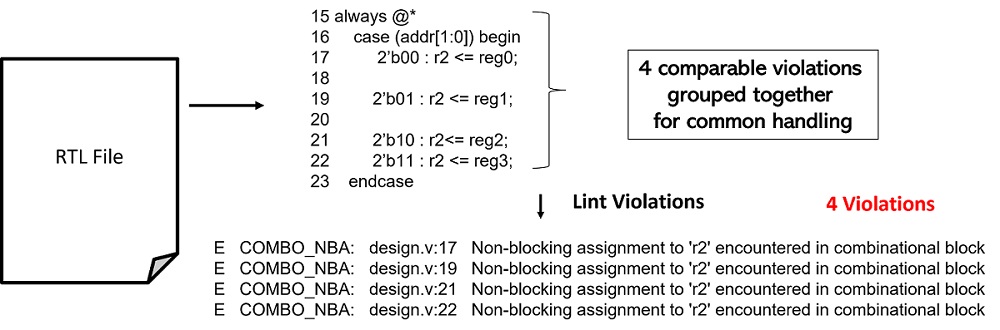

Low Noise Reporting

Ascent Lint provides the industry’s lowest noise RTL linting results. This means our reports dramatically minimize duplicate, irrelevant and false messaging. Additionally, our rules do not have the overlap found in older generation tools.

Our low noise reports mean engineers save time by avoiding wading through erroneous, duplicate, and poorly organized reports to try to identify which violations are real and which ones can be waived. Ascent Lint prioritizes errors so that fixes will produce the greatest improvement in the quality of the RTL or netlist.

Targeted Debug Accelerates Root Cause Analysis

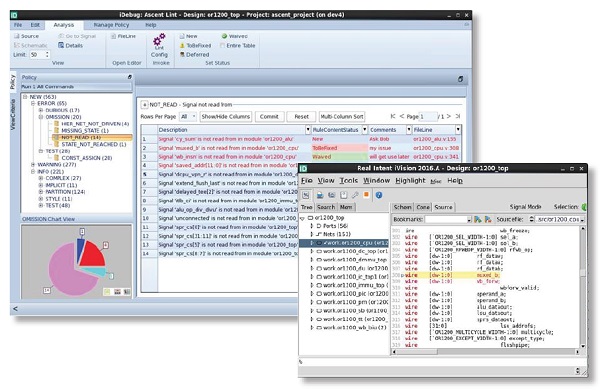

iDebug debugging platform enables custom views and cross probes to the RTL design source via a source browser or the integrated Emacs editor.

It also provides schematics to facilitate the debug of connectivity checks.

Real Intent’s iDebug environment also enables easy waiving and other status tracking.

Ascent Lint enables highly targeted debug:

- User-customizable severity levels — designers can specify custom naming for up to four different levels.

- Violation filtering — by file or their design module scope. Additional filtering is also available to further isolate areas of interest.

- Automatic grouping of related results for common handling — for example, when the same violation occurs multiple times within a block, or the violations have a common root cause.

- Violation sorting — to efficiently prioritize their debug effort, designers can sort the violations by severity level, status, rule, design location for proximity analysis, and details.

- Keyword searching — to instantly identify selected elements beyond the tool’s sorting factors.

What Ascent Lint Users are Saying

Fast

“The install and bring up for Real Intent’s Ascent Lint was extremely easy. We were able to deploy it with one engineer, and it took only one to two days to get to actionable data.

“Ascent Lint’s performance was fast, plus its outputs were clear and obvious — the ease of interpretation of results spoke to a mature tool. We look forward to using Ascent Lint on all of our future projects.

– Ty Garibay, VP of Engineering, Mythic

Design Intent

![]()

“What we really use Ascent Lint for is to identify where the designer’s intent deviates from his/her code. It’s able to look at a particular structure and say: I see what you’re doing, but this is what’s actually going to happen. Is that really what you want?

“It could be something as subtle as a width mismatch, such as trying to assign a 64-bit quantity only 62 bits and discovering that two bits are missing. Or inferred latches.”

– Semiconductor Designer, DeepChip.com EDA tool report

Precision, Low Noise

“Ascent Lint RTL linter is low noise, it only reports errors and warnings that are real. Other lint tools can generate a lot of garbage, which makes it hard to sort through.

“Also, it helps a lot that Ascent Lint’s reports do not have duplicates. Some of the other tools can give you the same error – with different names — 2, 3, 4, and even 20 times. Real Intent’s company name makes the point — they try to figure out your real intent for your design.”

– Semiconductor Designer, DeepChip.com EDA tool report

Efficient Debug

![]()

“Hailo used Ascent Lint for RTL linting sign-off for its edge AI processor. The tool ramp-up was fast – only a couple of weeks. Additionally, Hailo found multiple design issues, and shorten their design and verification time.

“Ascent Lint shortened our verification time an estimated five weeks by reducing simulation debug time. The Real Intent tools were able to scale up well with a high number of layers.”

– Guy Kaminitz, Hailo, Case Study

What is RTL Linting?

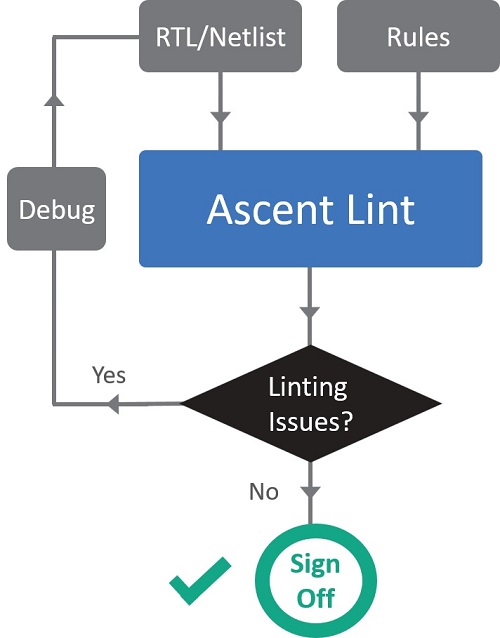

RTL Linting RTL Linting uses automated structural analysis to verify adherence to specified design coding rules that prevent synthesis issues & functional bugs and enforce coding styles for readability & re-use. RTL linting is run before simulation and following design changes, until final linting sign-off.

Key Takeaways: Ascent Lint RTL Linting Sign-Off

This section summarizes how Ascent Lint, the industry-leading RTL linting sign-off solution, delivers the lowest-noise linting results in the industry — eliminating the duplicate violations, false messages, and overlapping rules that slow SoC design teams down.

- Product. Ascent Lint is the industry-leading RTL linting sign-off solution, using static analysis to enforce coding guidelines and catch functional issues before simulation — reducing risk throughout the SoC design cycle.

- Key Challenge. RTL designs accumulate syntax errors, semantic violations, and coding style issues that simulation alone cannot efficiently detect; Ascent Lint surfaces these precisely and early, preventing costly downstream re-spins.

- Competitive Advantages. Ascent Lint delivers the industry’s lowest-noise linting results, eliminating the duplicate violations, false messages, and overlapping rules that burden engineers in other RTL linting tools.

- Design Flow Fit. Ascent Lint fits naturally at the earliest stages of RTL development and remains the primary check for design integrity through final sign-off, supporting Verilog, SystemVerilog, and VHDL — including encrypted third-party IP per IEEE 1735 — and scaling to the largest, most complex SoC designs.

- Engineering Benefits. Engineers deploy Ascent Lint in one to two days and reach actionable results immediately, with some users reporting verification cycles shortened by as much as five weeks due to reduced simulation debug time.

- Ecosystem. Ascent Lint integrates into existing design flows across all major EDA environments and is ISO 26262 certified by TÜV SÜD, enabling immediate adoption into automotive functional safety flows without additional qualification overhead.