Case Study Presentation Overview

Dr Yong Lee SK Hynix Inc., Sungnam, Republic of Korea, presented a case study on SK Hynix’s advanced reset domain crossing methodology and verification, using Real Intent Meridian RDC (reset domain crossing).

Dr. Lee presented results that using proactive methodology with the right set of static RDC sign-off tools reduced user reset design crossing verification effort from 2 weeks to only 25 mins.

He also stated this is the first time in recent memory where SK Hynix didn’t have any reset related issues on the first silicon.

(The PDF case study version has additional details.)

SK Hynix Reset Design Challenges

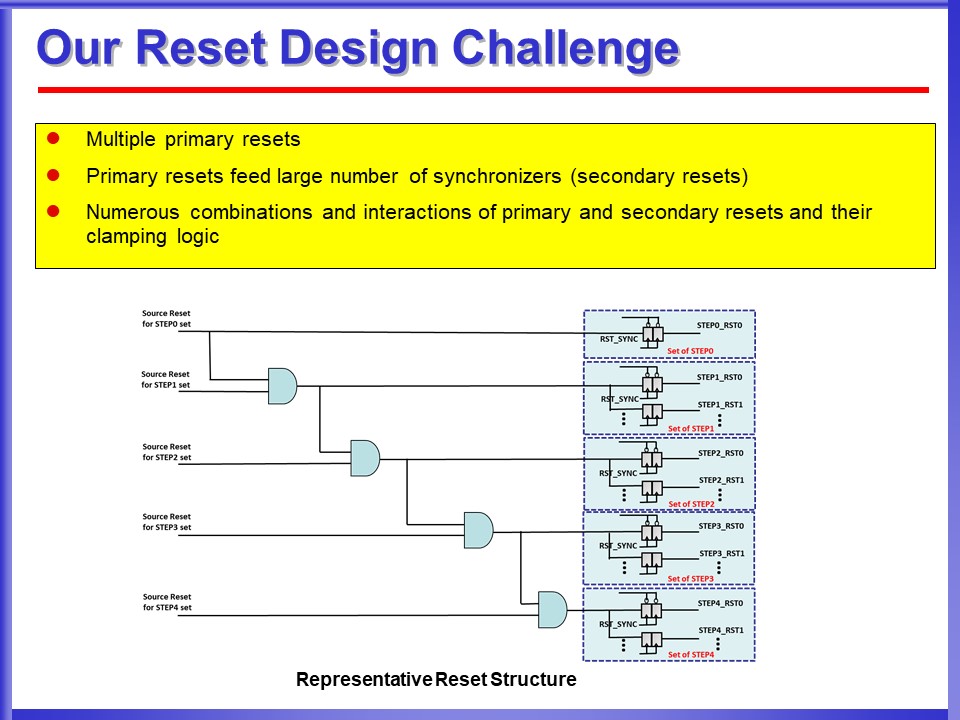

This slide shows SK Hynix’s simplified reset scheme.

- STEP0 is the power reset.

- STEP1 is the software reset.

- STEP2 is the global IP reset.

- STEP3 is a more detailed IP reset.

- STEP4 is debug reset.

Multiple primary resets feed large number of synchronizers that will be used independently with individual clamping logic.

SK Hynix RDC Verification Challenges

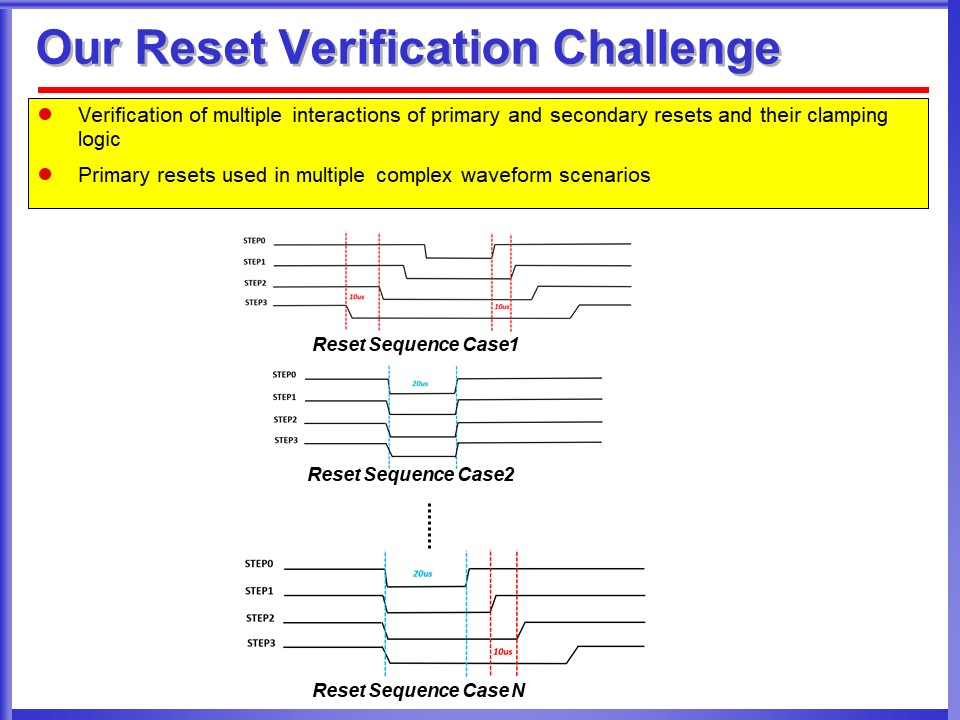

SK Hynix’s major challenge for their device relates to supporting multiple interaction types and waveform specifications between primary and secondary resets.

The slide shows three example cases that SK Hynix supports.

- Case2 shows a sequence where all the resets are asserted and de-asserted with power resets.

- Case3 shows a sequence where assert happens with power reset whereas de-assert is at different times.

As a result of these multiple resets and such complex scenarios, it has been difficult for them to create a sign-off flow for resets.

Traditional RDC Verification Approach Limitations

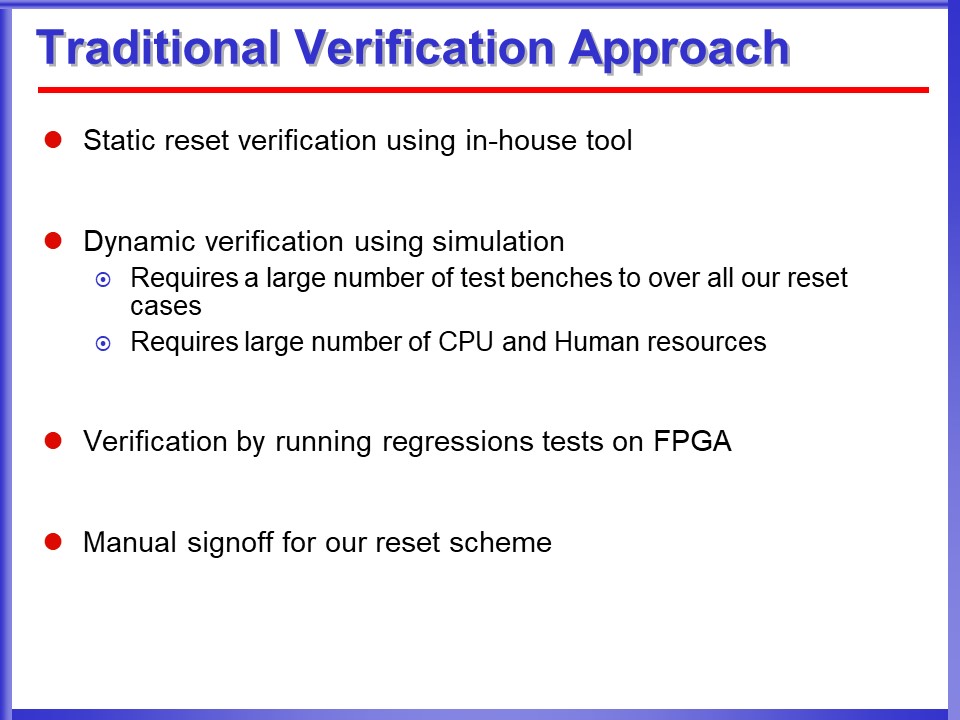

SK Hynix used to verify this problem using an existing commercial RDC static analysis tool, plus dynamic verification using simulation and regression tests on FPGAs.

Additionally, a thorough manual review was also done for all reset schemes.

The existing static tools required a huge setup effort; SK Hynix had to define resets on all reset synchronizers for their design.

Further, this method could not cover multiple reset scenarios, so designers spent a lot of time just reviewing the false violations. It also required a major effort to complete reset verification.

New Reset Domain Crossing Sign-Off Methodology

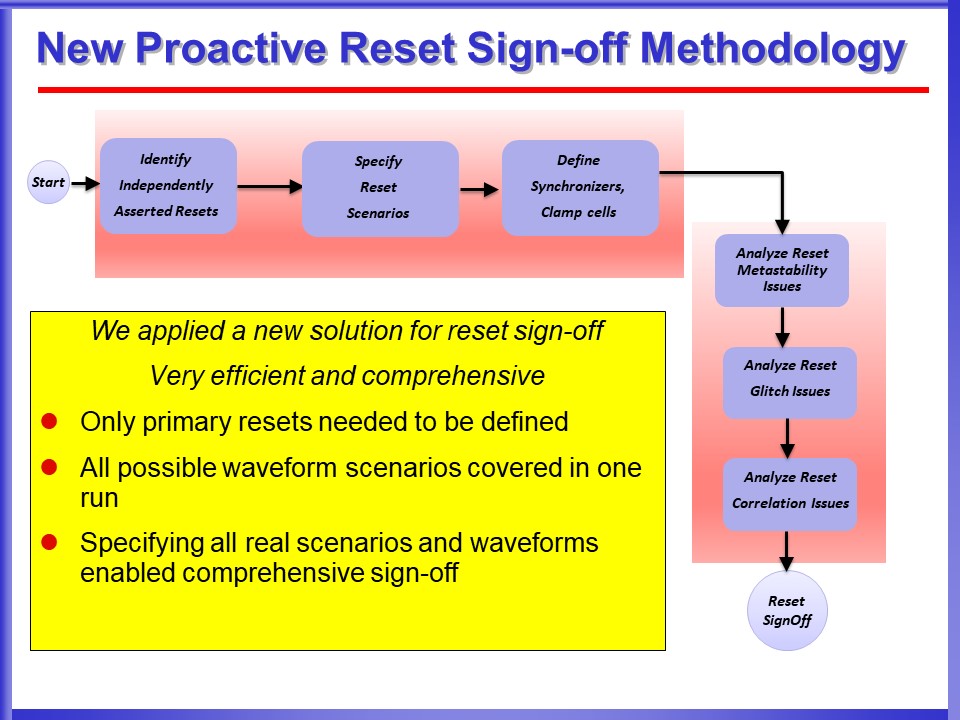

SK Hynix’s new methodology incorporated Real Intent’s Meridian RDC (reset domain crossing) tool.

SK Hynix’ goal was that their engineers would only define root resets and Meridian RDC tool would automatically propagate the resets through all the synchronizers, while handling multiple reset sequences throughout the design.

For reset setup with Meridian RDC, SK Hynix only needed to define primary independently asserted resets. They specified 3 reset scenarios and clamp and synchronizer cells for their verification.

After Meridian RDC generated results SK Hynix’s engineers focused on metastability issues due to soft resets.

With their previous methodology, primary reset propagation through the synchronizers were not handled with proper timing information. In contrast, Meridian RDC helped to identify important reset issues quickly and to make appropriate changes early in the flow.

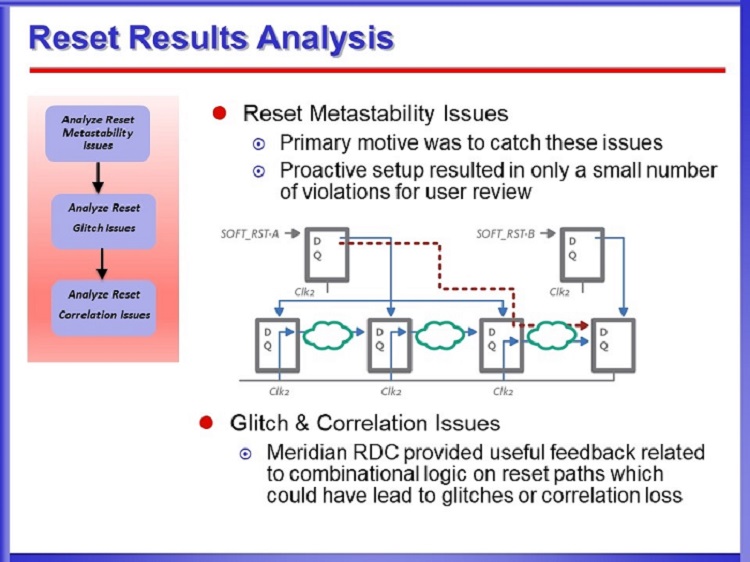

Reset Domain Crossing Analysis Findings

SK Hynix’s primary motive was to catch reset metastability issues.

This proactive setup process helped ensure that only a small number of violations were reported for users to manually review.

Additionally, Meridian RDC also pointed to useful issues related to combinational logic on reset paths; these would have led to glitches or correlation loss in the design if they had not been identified,

Comparing New RDC Methodology to Prior Approach

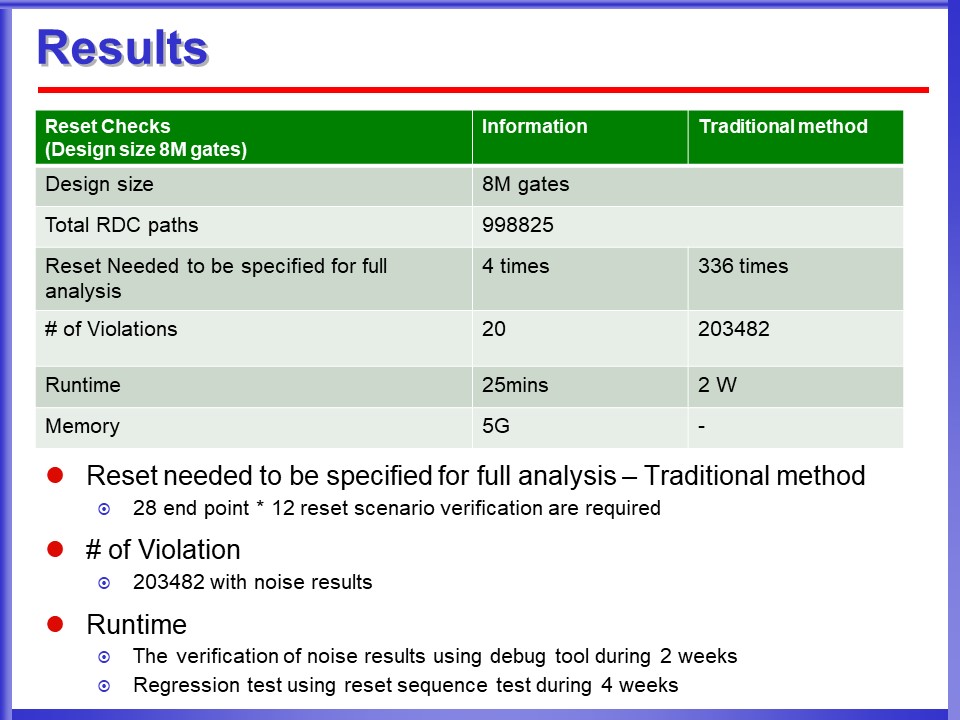

SK Hynix’s design size was around 8 million logic gates.

The total number of RDC paths for this design was 998,825.

- With the traditional commercial RDC static analysis tool, SK Hynix had to define 336 resets domains based on 28 endpoint resets and 12 reset scenarios.They had to run verification many times to verify all these reset scenarios.

- With Real Intent Meridian RDC, SK Hynix only needed to specify 4 resets. The rest was taken care of automatically by the tool.

- The traditional commercial RDC static analysis tool reported 203, 482 violations. SK Hynix was required to use many engineers to debug all these violations, because if even one of the errors was real, the chip would require ECO changes.

- Real Intent Meridian RDC only reported 20 violations with only 25 minutes run time.

So, with the new approach with Meridian RDC, the run time came down from 2 weeks to 25 mins.

SK Hynix was able to run debug and complete sign-off in the same day, as compared with 2 weeks using their traditional method.

Conclusion: Achieved First Time Silicon Success for RDC

SK Hynix said that with their prior methodology, it had been difficult to verify reset aspects of SK Hynix’s design.

SK Hynix got very good turnaround time using their new methodology with Real Intent Meridian RDC.

They commented that Real Intent’s tool had good performance, it analyzed the reset domains very well, and allowed designers to guarantee robust reset design.

The most important aspect was that with their previous development process, SK Hynix had many reset issues in silicon.

With Meridian CDC, SK Hynix said they didn’t require any additional silicon fixes related to reset. The new methodology and tool enabled them to achieve good silicon results in the first iteration.