Real Intent Announces 10X+ Speedup & 5X Capacity Improvement for Ascent AutoFormal Formal Linting Product

AutoFormal Expands on Ascent Lint Early Functional Verification to Further Reduce Simulation Effort

SUNNYVALE, Calif., June 25, 2019 — Real Intent, Inc., today announced that Ascent AutoFormal formal linting tool has been improved to provide 10X+ performance gains and analyze 5X larger designs when compared to the previous version. Customers can now quickly achieve early RTL verification of multimillion gates prior to simulation.

This release offers the following new features:

- Faster runtime & higher capacity — resulting from a combination of a 5-10x speedup of Ascent AutoFormal’s single core engine plus a 2-4X speedup from the automatic splitting of runs across parallel cores. (The 2-4x speedup estimate is based on a nominal 8 cores.)

- Extremely high completion rate — the new engines dynamically determine whether or not the analysis is converging for a particular check and move on to a new check when necessary.

- Reduced turnaround time — detailed RTL design information that can impact the formal analysis is automatically provided prior to the tool running the formal analysis. This ensures that relevant design elements are accurately analyzed in the first formal run, reducing iterations. For example, in addition to clocks and resets, the tool recognizes FSMs, and also identifies elements such as latches that could prevent the detection of the FSMs.

“Real Intent’s enhanced Ascent AutoFormal is part of our new generation static sign-off tools that provide customers with the necessary precision and speed to meet aggressive time-to-market deadlines,” said Prakash Narain, Real Intent’s president and CEO. “Multiple customers are already using Ascent AutoFormal in a production capacity and benefiting from the additional simulation time reduction that the tool’s early functional verification delivers.”

About Ascent AutoFormal

Ascent AutoFormal’s formal linting identifies RTL design bugs early using formal sequential design analysis. AutoFormal finds RTL bugs early in the design flow, before test benches are available, making debug easier, and eliminating lengthy, costly chip-level simulation cycles.

AutoFormal automatically generates functional assertions based on implied design intent, eliminating the need for designers to learn an assertion language and manually create potentially 1000s of assertions. Examples are FSM deadlocks, and coverage issues such as code reachability, constant nets, and constant assignments.

Additionally, the tool’s hierarchical root-cause analysis minimizes debug by uncovering the root cause of bugs deep in a design. Ascent AutoFormal determines and separately classifies: root-cause errors; secondary violations due to propagation of the root-cause error; duplicate errors from multiple instances; and structural violations that can be found by an RTL linter such as Ascent Lint.

The new AutoFormal release is commercially available immediately and can be used standalone or with an RTL linter. For more information, please visit Ascent AutoFormal formal linting.

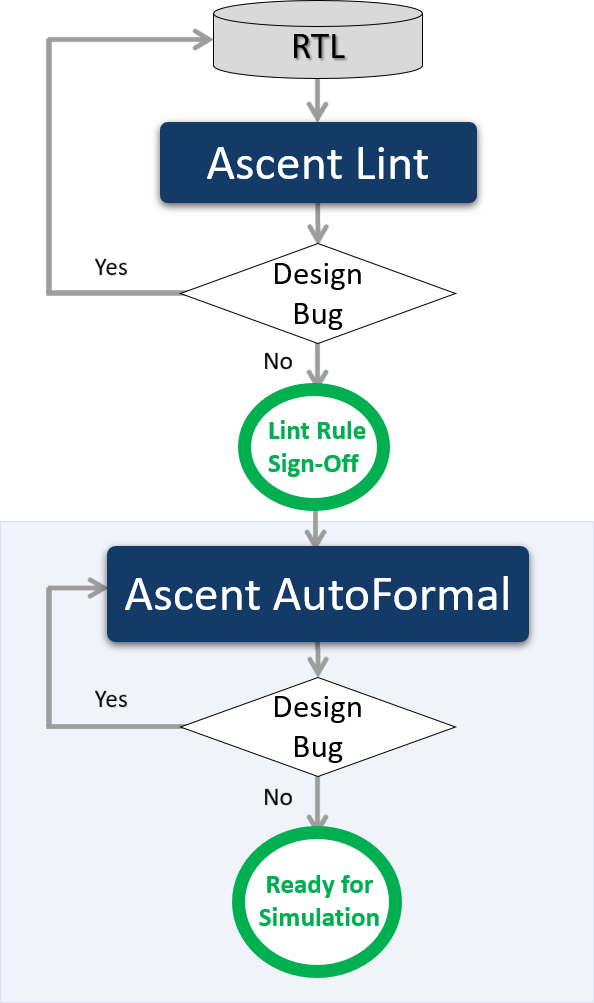

2-Step Early Functional Verification with Ascent Lint & Ascent AutoFormal

About Real Intent

Real Intent provides intent-driven static signoff software tools to accelerate early functional verification and advanced sign-off of digital designs. The company’s current offerings are: clock domain crossing sign-off from RTL through gate level, including multimode CDC; reset domain crossing sign-off; X-verification; advanced RTL linting; and automatic RTL verification. Real Intent products lead the market in precision, performance, and capacity. Real Intent customers include more than 50 major semiconductor and systems companies. Real Intent is headquartered at 932 Hamlin Court, Sunnyvale, CA. For more information visit us at www.realintent.com (or jp.realintent.com in Japan).