Dynamic CDC Verification for Memory Design

Case Study by Inryoul Lee, Principal Engineer of Samsung

Case Study Overview

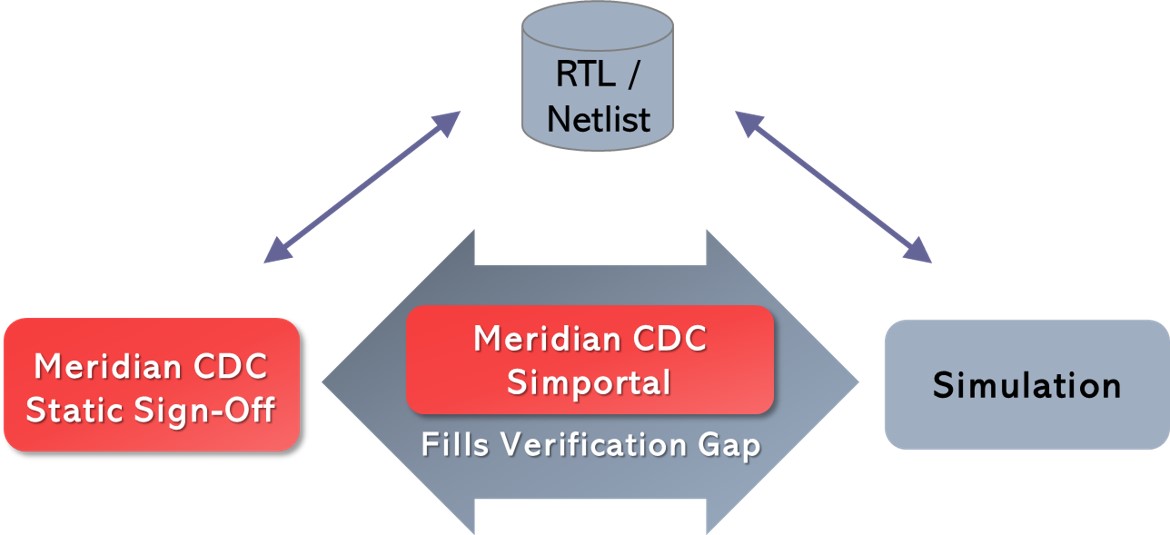

Inryoul Lee discusses how Samsung implemented their advanced dynamic clock domain crossing verification methodology for memory design using Real Intent Meridian CDC Simportal, closing the sign-off gap between CDC static sign-off and simulation. Slightly edited transcript below.

I. Closing gap between CDC static sign-off & simulation

Samsung partnered with Real intent to implement our advanced dynamic CDC verification methodology for memory design using Meridian CDC Simportal.

There has been a missing correlation between CDC static sign-off and simulation.

To close this sign-off gap, Samsung runs simulations that functionally exercise the clock domain crossing — including modeling metastability and its effects.

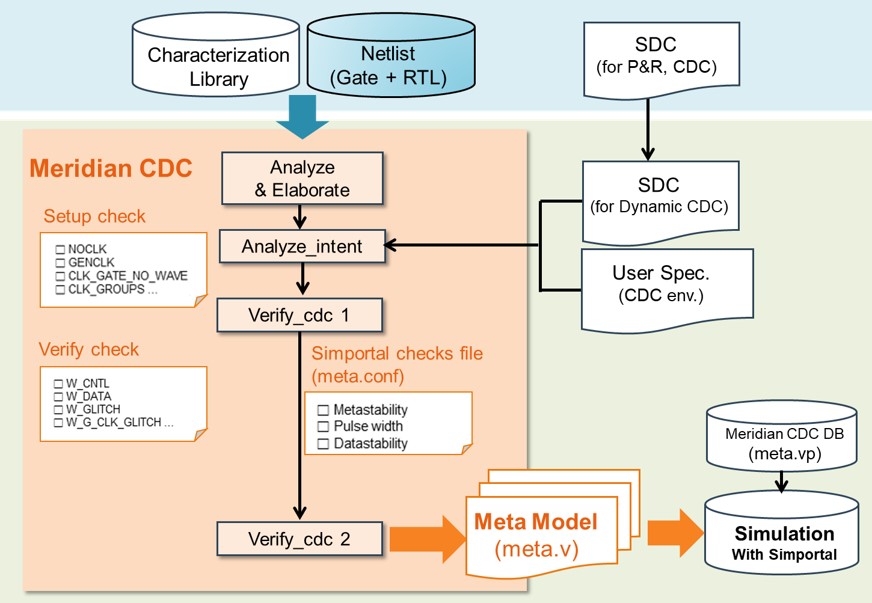

II. Dynamic clock domain crossing verification workflow

Our key steps for our new dynamic CDC verification flow with Meridian Simportal are:

- First, we provide our RTL and gate-level netlist memory design input. Real Intent’s Meridian CDC static sign-off tool analyzes and elaborates the design.

- During the Analyze Intent step, the tool assesses whether setup is complete – including identifying missing input file constraints.

- During ‘Verify CDC part 1’, the tool creates the structural CDC violations report. Plus, it generates a corresponding metastability-aware model to be used in simulation.

- Samsung ports metastability-aware models that Simportal generates to our simulator for running our regression test cases.

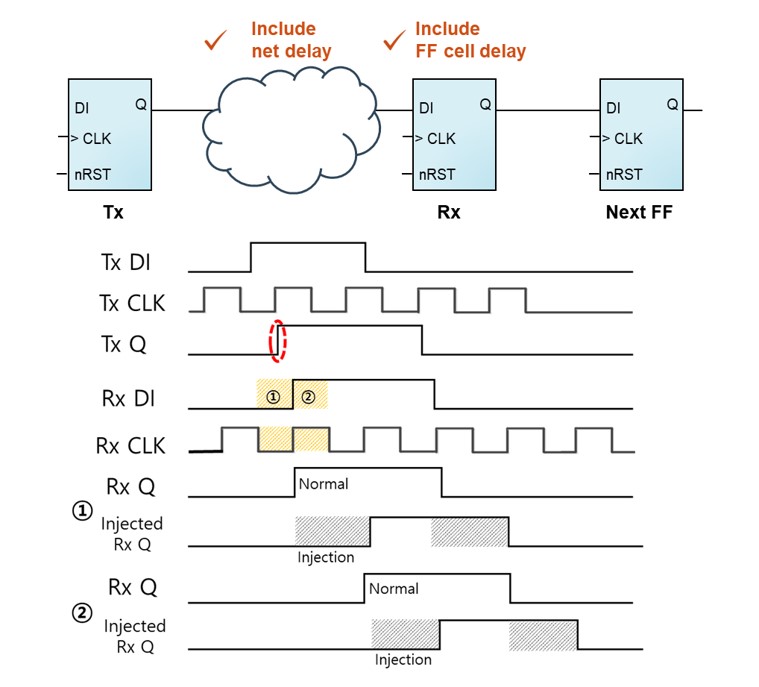

III. Gate-level dynamic CDC verification

Samsung worked closely with Real Intent to enhance dynamic CDC verification for memory design in two primary ways.

First, Meridian CDC added gate-level netlist support for our dynamic CDC verification — in addition to the existing RTL support.

Our methodology now covers issues with gate level flop cell delay. For example, we can now catch hold violations related to gate level clock skew at the next flipflop.

It also includes the transmitter to receiver interconnect delay, to help account for early or late data arrival times.

Gate-level netlist support

IV. 5X improvement in simulation runtime & turnaround time

Second, 40% of memory design has asynchronous clock domains and interfaces – compared to only 1 percent for SOCs. So, we needed to optimize our design constraints and simulation runtime in data path.

Our design constraints in memory design have many clock definitions because of the timing guarantee. We reduced false errors by optimizing and grouping our clock definitions.

We achieved a 5X improvement in simulation run time and turnaround time for verifying all the data paths — by deleting and grouping data paths modeling files by function.

V. Case study: Error uncovered by Meridian CDC Simportal

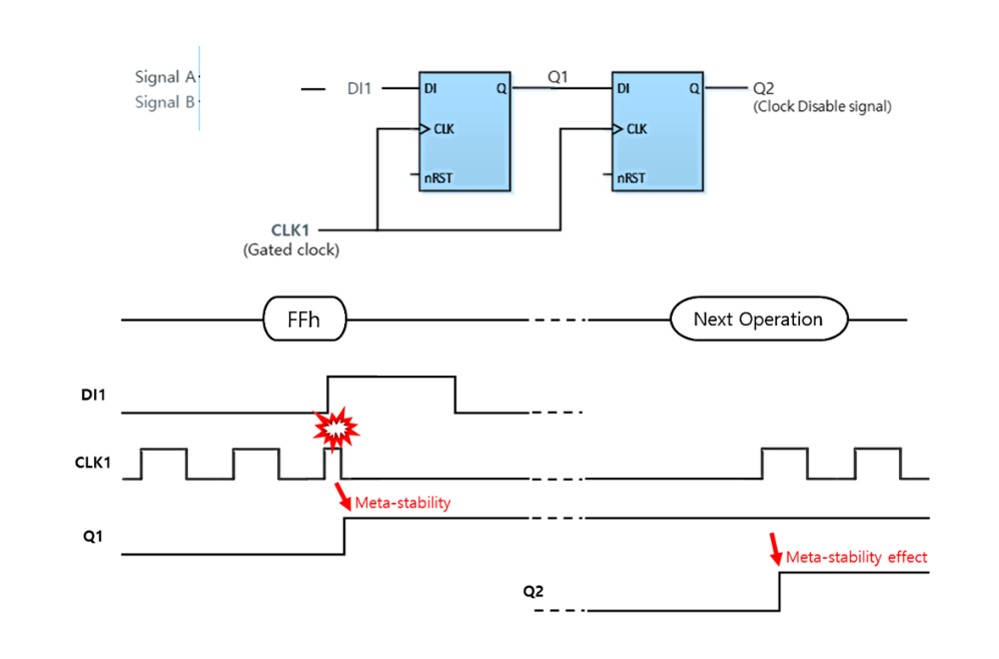

This drawing shows an example of an FSM (finite state machine) metastability error caught by our flow with Simportal. The Q2 transition was so high that the FSM was disabled, leading to a deadlock.

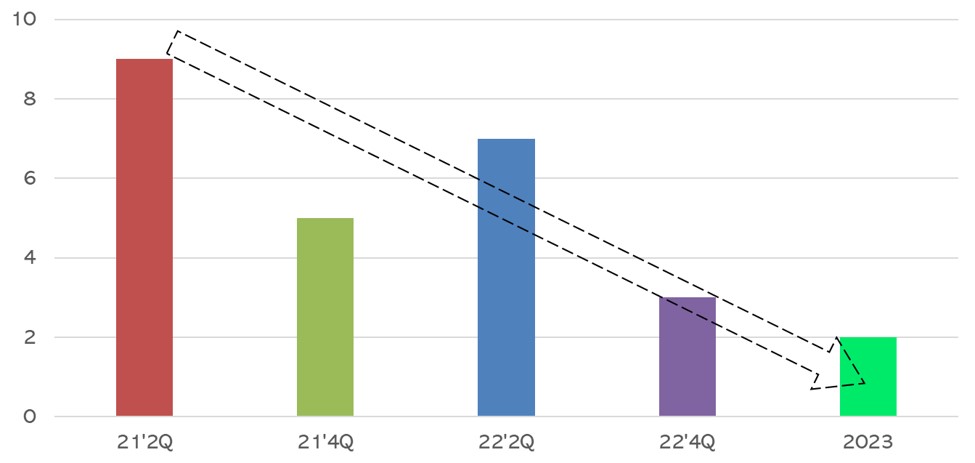

VI. Results: Major drop in memory product CDC issues

The result of our deploying our advanced dynamic CDC verification methodology with Meridian CDC Simportal have been remarkable in terms of catching critical design bugs.

This figure illustrates our major drop in memory product CDC issues.